- 您现在的位置:买卖IC网 > Sheet目录3881 > PIC18F8585T-I/PT (Microchip Technology)IC PIC MCU FLASH 24KX16 80TQFP

PIC18F6585/8585/6680/8680

DS30491C-page 334

2004 Microchip Technology Inc.

In Mode 1 and 2, there are a total of 16 acceptance fil-

ters available and each can be dynamically assigned to

any of the receive buffers. A buffer with a lower number

has higher priority. Given this, if an incoming message

matches with two or more receive buffer acceptance

criteria, the buffer with the lower number will be loaded

with that message.

23.7.3

ENHANCED FIFO MODE

When configured for Mode 2, two of the dedicated

receive buffers, in combination with one or more pro-

grammable transmit/receive buffers, are used to create

a maximum of 8 buffers deep FIFO (First In First Out)

buffer. In this mode, there is no direct correlation

between filters and receive buffer registers. Any filter

that has been enabled can generate an acceptance.

When a message has been accepted, it is stored in the

next available receive buffer register and an internal

write pointer is incremented. The FIFO can be a maxi-

mum of 8 buffers deep. The entire FIFO must consist of

contiguous receive buffers. The FIFO head begins at

RXB0 buffer and its tail spans toward B5. The maxi-

mum length of the FIFO is limited by the presence or

absence of the first transmit buffer starting from B0. If a

buffer is configured as a transmit buffer, the FIFO

length is reduced accordingly. For instance, if B3 is

configured as transmit buffer, the actual FIFO will con-

sist of RXB0, RXB1, B0, B1 and B2, a total of 5 buffers.

If B0 is configured as a transmit buffer, the FIFO length

will be 2. If none of the programmable buffers are con-

figured as a transmit buffer, the FIFO will be 8 buffers

deep. A system that requires more transmit buffers

should try to locate transmit buffers at the very end of

B0-B5 buffers to maximize available FIFO length.

When a message is received in FIFO mode, the Inter-

rupt Flag Code bits (EICODE<4:0>) in the CANSTAT

register will have a value of ‘10000’, indicating the

FIFO has received a message. FIFO pointer bits

FP<3:0> in the CANCON register point to the buffer

that contains data not yet read. The FIFO pointer bits,

in this sense, serve as the FIFO read pointer. The user

should use FP bits and read corresponding buffer data.

When receive data is no longer needed, the RXFUL bit

in the current buffer must be cleared, causing FP<3:0>

to be updated by the module.

To determine whether FIFO is empty or not, the user

may use FP<3:0> bits to access RXFUL bit in the cur-

rent buffer. If RXFUL is cleared, the FIFO is considered

to be empty. If it is set, the FIFO may contain one or

more messages. In Mode 2, the module also provides

a bit called FIFO High Water Mark (FIFOWM) in the

ECANCON register. This bit can be used to cause an

interrupt whenever the FIFO contains only one or four

empty buffers. The FIFO high water mark interrupt can

serve as an early warning to a full FIFO condition.

23.7.4

TIME-STAMPING

The CAN module can be programmed to generate a

time-stamp for every message that is received. When

enabled, the module generates a capture signal for

CCP1, which in turn captures the value of either Timer1

or Timer3. This value can be used as the message

time-stamp.

To use the time-stamp capability, the CANCAP bit

(CIOCAN<4>) must be set. This replaces the capture

input for CCP1 with the signal generated from the CAN

module. In addition, CCP1CON<3:0> must be set to

‘0011’ to enable the CCP special event trigger for CAN

events.

23.8

Message Acceptance Filters

and Masks

The message acceptance filters and masks are used to

determine if a message in the message assembly

buffer should be loaded into any of the receive buffers.

Once a valid message has been received into the MAB,

the identifier fields of the message are compared to the

filter values. If there is a match, that message will be

loaded into the appropriate receive buffer. The filter

masks are used to determine which bits in the identifier

are examined with the filters. A truth table is shown

below in Table 23-2 that indicates how each bit in the

identifier is compared to the masks and filters to deter-

mine if a message should be loaded into a receive

buffer. The mask essentially determines which bits to

apply the acceptance filters to. If any mask bit is set to

a zero, then that bit will automatically be accepted

regardless of the filter bit.

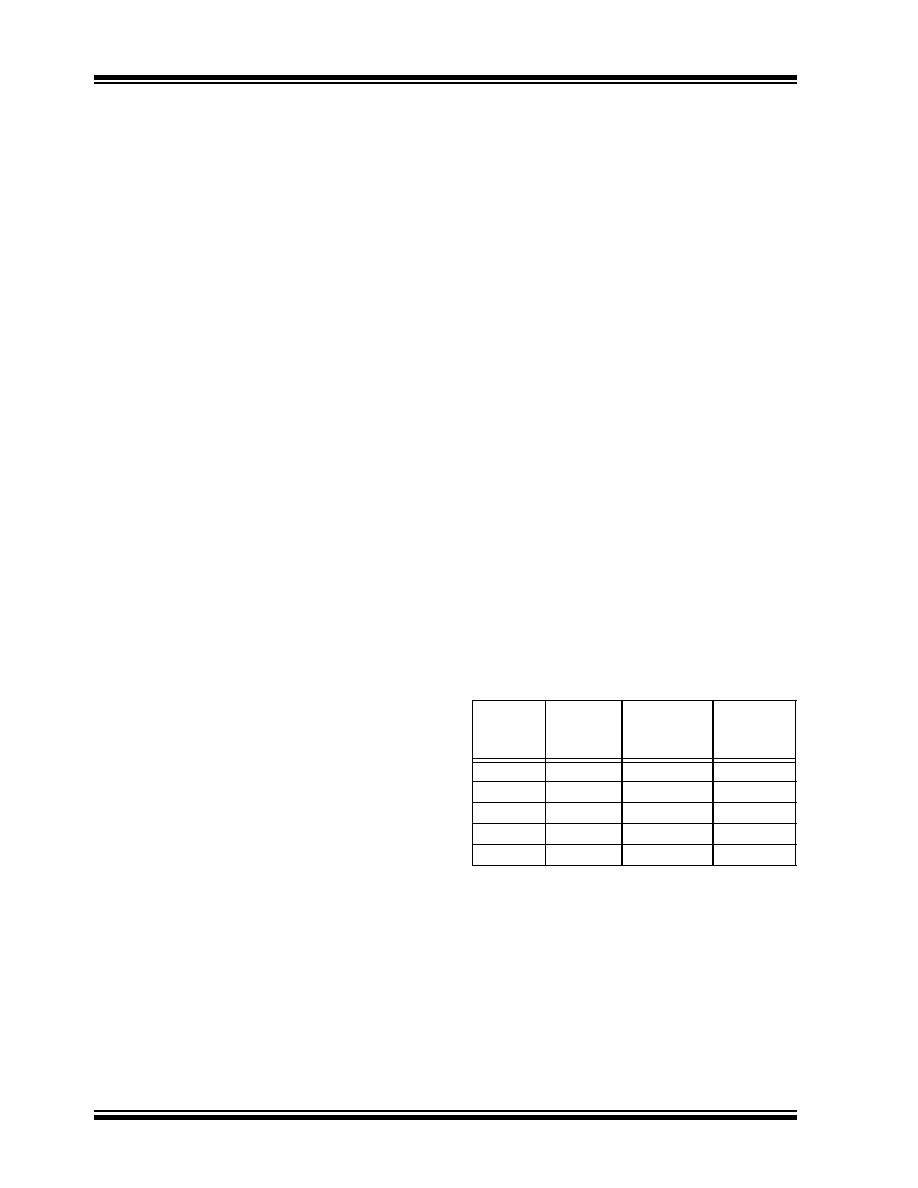

TABLE 23-2:

FILTER/MASK TRUTH TABLE

In Mode 0, acceptance filters RXF0 and RXF1 and filter

mask RXM0 are associated with RXB0. Filters RXF2,

RXF3, RXF4 and RXF5 and mask RXM1 are

associated with RXB1.

Mask

bit n

Filter

bit n

Message

Identifier

bit n001

Accept or

Reject

bit n

0x

x

Accept

10

0

Accept

10

1

Reject

11

0

Reject

11

1

Accept

Legend: x = don’t care

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

XF2J-2424-11

CONN FPC 24POS 0.5MM SMT

PIC18LF6585T-I/PT

IC PIC MCU FLASH 24KX16 64TQFP

PIC18LF6680T-I/PT

IC PIC MCU FLASH 32KX16 64TQFP

XF2J-2224-11

CONN FPC 22POS 0.5MM SMT

PIC18F6525T-I/PT

IC PIC MCU FLASH 24KX16 64TQFP

PIC18F4439-E/ML

IC PIC MCU FLASH 6KX16 44QFN

XF2J-2024-11

CONN FPC 20POS 0.5MM SMT

PIC16LF747-I/ML

IC PIC MCU FLASH 4KX14 44QFN

相关代理商/技术参数

PIC18F85J10-I/PT

功能描述:8位微控制器 -MCU 32 KB FL 2 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J10-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC18F 40MHZ TQFP-80 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC18F, 40MHZ, TQFP-80

PIC18F85J10T-I/PT

功能描述:8位微控制器 -MCU 32 KB FL 2 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J11-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 2048BRAM 67I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J11T-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 2048bytes-RAM 67I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J15-I/PT

功能描述:8位微控制器 -MCU 48 KB FL 4 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J15T-I/PT

功能描述:8位微控制器 -MCU 48 KB FL 4 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J50-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 3936byte RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT